那个被裁掉的“PPT架构师”,和那个涨薪50%的“打杂”工艺工程师

“你知道吗?2026年Q1,某头部晶圆厂因为一位资深工艺工程师优化了一道蚀刻工艺,将3nm某关键层的良率提升了3%,直接为公司季度净利润贡献了数千万美元。而同期,一个曾负责‘画大饼’式未来架构的团队,因技术路线无法落地,被整体裁撤。”

最近半导体圈里,一个对比鲜明的故事在工程师社群中流传甚广:一边是曾经风光无限、擅长用精美PPT描绘“颠覆性架构”的架构师黯然离场;另一边,是那些常年泡在产线、解决各种“脏活累活”的工艺工程师,不仅稳如泰山,薪资更是逆势大涨,有人甚至拿到了超过50%的涨幅。

这绝非偶然。它清晰地指向一个正在发生的行业深层变革:半导体行业,正在从追逐概念泡沫的“讲故事时代”,回归到尊重物理极限、敬畏制造细节的“硬核制造时代”。当摩尔定律逼近物理与经济的双重墙,每一纳米的进步都依赖于对工艺极致的雕琢时,谁在创造真实价值,一目了然。

01 行业转向:当“PPT”撞上“物理之墙”

过去几年,资本狂热催生了一种现象:某些团队依靠一个听起来“性感”的架构概念(如某种革命性的存算一体或类脑计算架构),就能获得巨额融资。他们的核心产出往往是几十页充满复杂框图和性能预测曲线的PPT,承诺在“不久的将来”实现数量级的能效比提升。

然而,2025-2026年的现实是,这些“未来架构”绝大多数卡死在了从PPT到硅片的“死亡之谷”里。原因无他:它们严重低估了半导体制造的复杂性与物理约束。

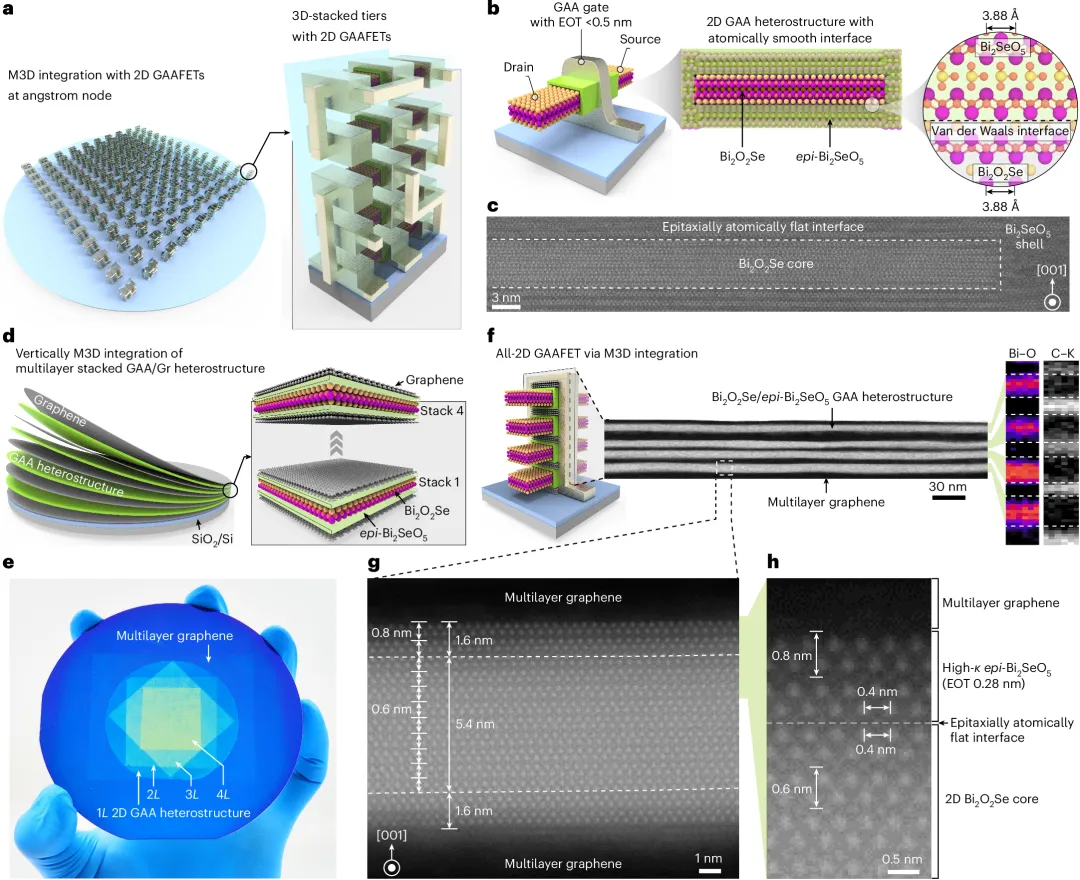

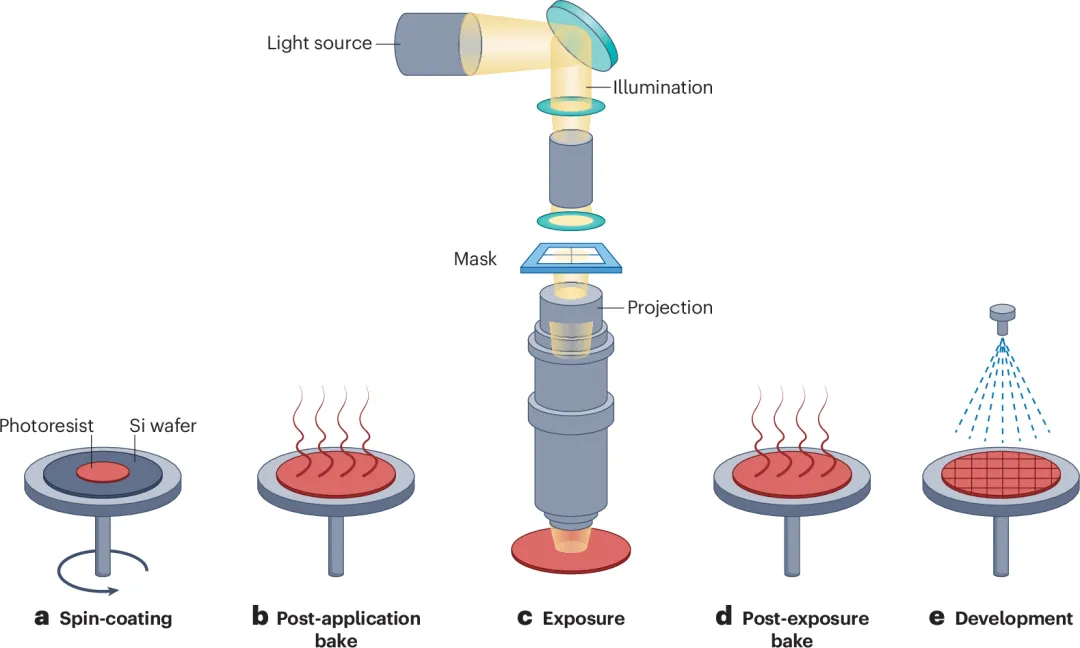

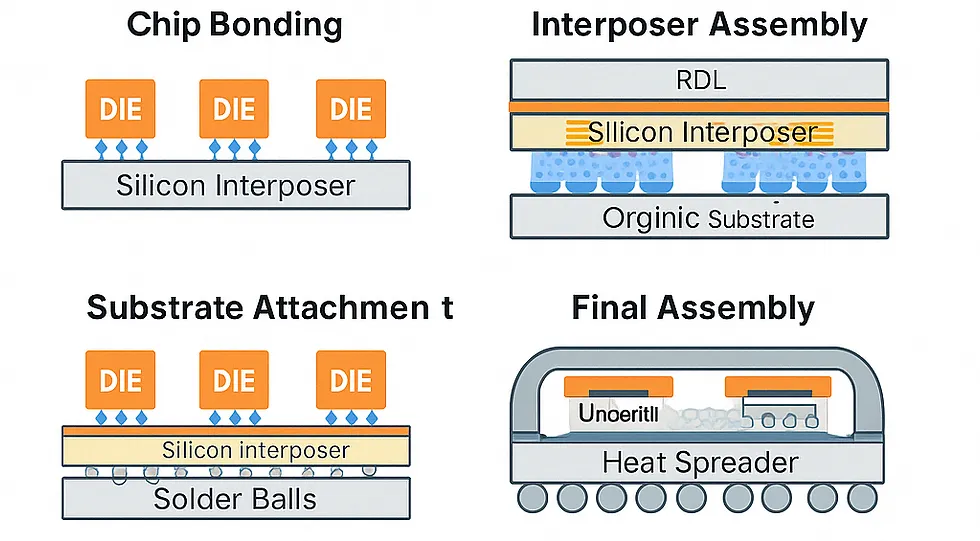

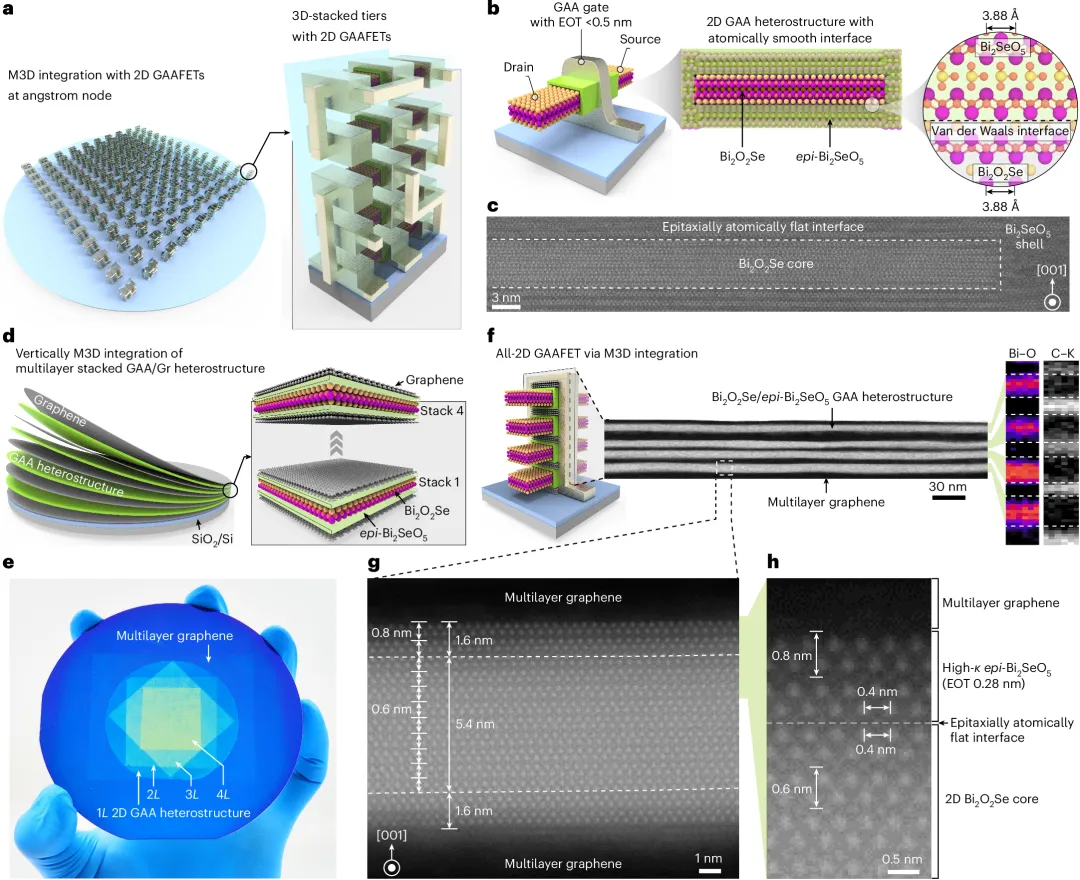

•制造决定性能上限:一个再精妙的架构,最终需要依托于晶体管、互连线、存储单元等物理实体来实现。3nm及以下制程的晶体管,其沟道可能只有几十个原子宽,任何微小的工艺波动(如掺杂不均匀、边缘粗糙度)都会导致性能的巨大离散。“架构是设计出来的,性能是制造出来的”,已成为行业共识。•成本与良率是生死线:根据SEMI 2025年Q4《全球晶圆厂展望报告》,建设一座月产5万片的3nm先进制程晶圆厂,成本已超过200亿美元。在此背景下,良率(Yield)直接等同于利润。一个无法在现有或可预见的工艺平台上实现高良率量产的架构,商业上毫无意义。•系统级瓶颈转移:随着Chiplet(芯粒)技术成为高性能计算的主流,系统的瓶颈从单一的芯片设计,转移到了封装、互连、散热和电源管理。这些无一不是高度依赖工艺和工程经验的领域。一个只会设计单颗芯片架构,却不懂先进封装(如台积电的CoWoS、英特尔的EMIB)中微凸点间距、热应力匹配的架构师,其设计价值大打折扣。行业的耐心正在耗尽。投资者和公司管理层开始追问:你的架构,在台积电N3P或英特尔18A工艺的设计规则手册(DRM) 里,如何实现?你的芯片,在2026年Q1的产线上,预估的初始良率(Initial Yield)是多少?需要多少轮次的光罩(Mask)和流片(Tape-out)才能达到可盈利的良率?

回答不了这些由制造工艺框定的硬核问题,“PPT架构师”的光环便迅速褪去。与此同时,那些能回答这些问题的人——工艺工程师,价值被重新发现和重估。

02 工艺工程师的“硬核”成长图谱

工艺工程师(Process Engineer),常被戏称为“打杂的”,因为他们需要处理从设备维护、工艺配方调试、缺陷分析到良率提升等看似琐碎却至关重要的问题。他们的成长,是一条与产线、数据和失败案例紧密捆绑的扎实路径。

阶段一:0-3年 —— “产线学徒”与“数据感知”

•核心状态:深入制造一线,在资深工程师指导下,负责某个单一工艺模块(如蚀刻、薄膜沉积、离子注入)的日常监控和基础维护。•核心挑战:将课本上的物理化学公式,与机台轰鸣声、硅片上的纳米级结构联系起来。理解何为工艺窗口(Process Window)、统计过程控制(SPC)图表的每一个异常波动意味着什么。•必备技能:1.设备原理:读懂你负责的机台手册,明白等离子体如何产生、前驱体如何分解沉积。2.基础数据分析:使用JMP、Excel等工具,分析工艺参数(如温度、压力、功率)与输出结果(如膜厚、均匀性、关键尺寸)的相关性。3.缺陷识别:在扫描电子显微镜(SEM)或光学显微镜下,能初步分辨颗粒污染、图形缺陷等。•2026年市场参考薪资区间(中国一线城市/新一线晶圆厂):年薪 25万 - 45万 人民币。起点差异取决于学历背景(博士起薪显著高于硕士)和所在工厂的技术水平(先进制程厂高于成熟制程厂)。阶段二:3-7年 —— “模块专家”与“问题猎手”

•核心状态:独立负责一个工艺模块的整合与优化,成为该领域的“活字典”。开始主导小型的工艺改进项目。•核心挑战:解决复杂的、跨变量的工艺问题。例如,为何某批次的晶圆在蚀刻后关键尺寸(CD)总是偏大?需要系统性地设计实验(DOE),隔离出关键影响因子。•必备技能:1.高级实验设计(DOE):熟练运用田口方法、响应曲面模型等,以最少的实验次数找到最优工艺参数组合。2.根因分析(RCA):运用鱼骨图、5 Why分析法等,对产线上突发的良率暴跌进行系统性溯源,可能是材料、设备、环境或人为操作问题。3.跨部门协作:与整合工程师(Integration)、器件工程师(Device)、良率工程师(YE)紧密合作,因为你的工艺问题可能源自上游,或会影响到下游。•2026年市场参考薪资区间:年薪 45万 - 80万 人民币。此时,是否具备解决重大良率事故的经验、是否有成功的工艺改进项目(如将某步骤的工艺耗时缩短10%以上)成为薪资分水岭。阶段三:7年以上 —— “工艺架构师”与“制造智者”

•核心状态:视野超越单一模块,参与甚至主导新工艺技术平台的开发与导入(如从FinFET向GAAFET的迁移)。能够从制造角度,反向定义设计规则,为电路设计团队提供“可制造性设计(DFM)”的约束建议。•核心挑战:在技术路线交叉口做出决策。例如,为了达到更小的晶体管间距,是采用EUV双重图形化(EUV Double Patterning),还是开发更复杂但次数更少的EUV单次成像技术?这需要对成本、周期时间、良率学习曲线进行综合建模预测。•必备技能:1.技术前瞻与评估:持续跟踪IMEC、SEMATECH等研究机构及竞争对手(台积电、三星)的技术路线图,评估新技术(如High-NA EUV、CFET)在本厂落地的可行性与风险。2.成本与良率建模:建立复杂的模拟模型,预测新工艺的成本 per wafer(每片晶圆成本) 和 良率 learning curve(良率学习曲线)。3.生态构建:与设备商(如AMAT、LAM)、材料商(如信越、陶氏)共同开发下一代工艺解决方案,甚至参与定制设备的规格定义。•2026年市场参考薪资区间:年薪 80万 - 200万+ 人民币。顶尖人才往往享有股票期权和项目奖金。他们的价值不仅在于解决已知问题,更在于规避未来可能发生的、代价高昂的技术风险。 | | | |

| 0-3年 | | 监控机台报警,处理日常工艺偏移,在指导下完成简单DOE。 | |

| 3-7年 | 高级DOE、复杂根因分析(RCA)、跨模块问题协同解决 | 独立负责良率问题调查,主导工艺优化项目,与整合/器件工程师频繁会议。 | |

| 7年以上 | 新技术路线评估、成本/良率建模、定义设计规则与DFM | 参与决定下一代工艺节点技术选项,与设备商共同开发新工艺,为设计团队制定制造约束。 | |

03 技能跃迁:从“操作员”到“制造战略家”的书单

工艺工程师的成长,离不开持续学习。以下书单与成长阶段相匹配,旨在构建从实践到理论,再从理论反哺实践的完整知识体系:

1. 奠基期(0-3年):建立物理直觉与工程思维

•《半导体制造技术》 (作者:Michael Quirk, Julian Serda)•为什么读:这是半导体制造的“百科全书”式教材。涵盖从晶圆制备到封测的全流程,语言相对平实。它能帮你快速建立对整个产业链的宏观认知,明白自己所在的工艺环节处于什么位置。•《芯片制造——半导体工艺制程实用教程》 (作者:Peter Van Zant)•为什么读:更侧重于实践操作和工艺细节。书中对每一道工艺步骤的机台、参数、常见问题都有细致描述,是解决日常问题的实用参考书。2. 升华期(3-7年):掌握深度分析与解决问题的方法论

•《实验设计与分析》 (作者:Douglas C. Montgomery)•为什么读:工艺优化的核心武器。这本书系统阐述了DOE的统计原理与方法,从简单的因子实验到复杂的响应曲面设计。吃透它,你设计实验的效率和对结果的解读能力将脱胎换骨。•《半导体器件物理与工艺》 (作者:施敏)•为什么读:工艺的最终目的是制造出合格的器件。施敏先生的这本经典著作,能让你从物理本质理解晶体管是如何工作的,以及工艺参数(如掺杂浓度、栅氧厚度)如何直接决定器件的电学特性(阈值电压、漏电流)。这是你从“操作工艺”走向“理解工艺”的关键一跃。3. 战略期(7年以上):洞察技术趋势与商业本质

•《VLSI制造原理》 (作者:S. M. Sze)•为什么读:更深入、更理论化。探讨深亚微米及纳米尺度下制造工艺面临的物理极限和挑战(如量子隧穿、迁移率退化)。适合用于研究前沿技术问题。•定期研读行业报告与技术白皮书•必读来源:•SEMI 季度/年度全球晶圆厂预测、设备材料市场报告。•台积电、三星、英特尔 年度技术研讨会资料及公开的技术白皮书(如台积电的《Technology Portfolio》)。•IMEC 年度技术路线图展望。•为什么读:保持对行业技术演进、产能布局、资本开支方向的敏感度。将自身工作置于全球产业大图景中,理解公司决策背后的商业逻辑。

04 回归本质:工艺即壁垒,制造即战略

“PPT架构师”的退场与“打杂”工艺工程师的崛起,共同宣告了一个旧时代的结束和一个新时代的开始。这个新时代的特征是:

1. 壁垒的重构:半导体行业的竞争壁垒,正从单纯的芯片设计能力,重构为“工艺实现能力”。谁能以更高的良率、更低的成本、更快的速度,将先进设计转化为实实在在的硅片,谁就掌握了产业链的制高点。

2. 价值的重估:行业开始用最朴素的尺度衡量价值——你是否解决了真实世界中的一个物理或工程问题,从而提升了性能、降低了成本或提高了良率? 工艺工程师每天的工作,都在直接回答这个问题。

3. 心态的回归:它呼唤一种**“工程师文化”的回归**:敬畏技术、崇尚实干、尊重细节、容忍失败并从中学习。这种文化,正是半导体产业从无到有、攻克无数技术难关的原始基因。

“过去十年,我们或许高估了架构创新能带来的短期突破;未来十年,我们绝不会低估工艺制造所蕴含的长期价值。” 一位国内头部芯片设计公司的CTO在2026年SEMICON China的一场闭门会议上如是说。

对于每一位半导体从业者而言,这既是警示,也是指南。它提醒我们,无论头衔多么炫目,最终都要接受制造现场的检验。它也指引我们,沉下心来,扎根于那些看似“打杂”的硬核领域,因为那里正孕育着这个行业下一个十年最坚实的竞争力。

为什么你的电车还在用90nm芯片,而英伟达Rubin已用上1.6nm?

晶圆厂涨价10%只是开胃菜?芯片通胀背后的“成熟制程陷阱”正在引爆

1nm“记忆开关”刷屏,但别急着欢呼:从实验室到替代“存算墙”,我们差几步?